# SAIA®PLC Programmable controllers

# Manual of the software level 1 H

English adition 06/704 E4

# **SOFTWARE LEVEL 1H**

PART D INTRODUCTION

PART E INSTRUCTION SET AND PROGRAMMING

PART F PROGRAMMING EXAMPLES

| TABLE OF CONTENTS                                                  |                                                                                                                                                                                                                                                                                                            |                                                      |  |  |

|--------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|--|--|

| PART D                                                             | INTRODUCTION                                                                                                                                                                                                                                                                                               | Page                                                 |  |  |

| D 1                                                                | General General                                                                                                                                                                                                                                                                                            | 1D                                                   |  |  |

| D 2                                                                | The program line                                                                                                                                                                                                                                                                                           | 2D                                                   |  |  |

| D 3<br>D 3.1<br>D 3.2                                              | The operands<br>Element addresses<br>Step addresses                                                                                                                                                                                                                                                        | 3D<br>3D<br>3D                                       |  |  |

| D 4<br>D 4.1<br>D 4.2<br>D 4.3                                     | Further definitions The linkage line The accumulator = ACCU Normally-open/normally-closed contacts or high/low                                                                                                                                                                                             | 4D<br>4D<br>4D<br>5D                                 |  |  |

| D 5<br>D 5.1<br>D 5.2<br>D 5.3<br>D 5.4                            | Programming methods Programming by ladder diagram Programming by logic diagram Programming by flowchart Combined programming by flowchart/logic or in accordance with Grafcet Programming with parallel programs                                                                                           | 7D<br>7D<br>8D<br>9D<br>10D                          |  |  |

| D 5.6<br>D 5.7                                                     | Programming with subroutines Address indexing (series processing)  INSTRUCTION SET AND PROGRAMMING                                                                                                                                                                                                         | 12D<br>13D                                           |  |  |

| E 1                                                                | Interrogation and linkage instructions                                                                                                                                                                                                                                                                     | 1E                                                   |  |  |

| E 2                                                                | Switching instructions                                                                                                                                                                                                                                                                                     | 8E                                                   |  |  |

| E 3<br>E 3.1<br>E 3.2<br>E 3.3<br>E 3.4<br>E 3.5<br>E 3.6<br>E 3.7 | Timing and counting instructions Transfer and arithmetic instructions Timers and counters Transfer instructions of binary and BCD-values External input of values in BCD-format Extended instructions STR, SCR Codes for arithmetic operations Summary of all instructions for timer and counter registers | 12E<br>12E<br>13E<br>17E<br>18E<br>19E<br>20E<br>21E |  |  |

| E 4                                                                | Jump and wait instructions                                                                                                                                                                                                                                                                                 | 22E                                                  |  |  |

| E 5                                                                | Auxiliary instructions                                                                                                                                                                                                                                                                                     | 28E                                                  |  |  |

| E 6                                                                | Indexing                                                                                                                                                                                                                                                                                                   | 30E                                                  |  |  |

| E 7                                                                | PAS-instructions                                                                                                                                                                                                                                                                                           | 35E                                                  |  |  |

| E 8                                                                | Display instructions                                                                                                                                                                                                                                                                                       | 39E                                                  |  |  |

| PART F                                                             | PROGRAMMING EXAMPLES                                                                                                                                                                                                                                                                                       | 1F                                                   |  |  |

| Frocedure to                                                       | r solving a control problem by the introduction of a PLC                                                                                                                                                                                                                                                   | 38F                                                  |  |  |

# PART D INTRODUCTION

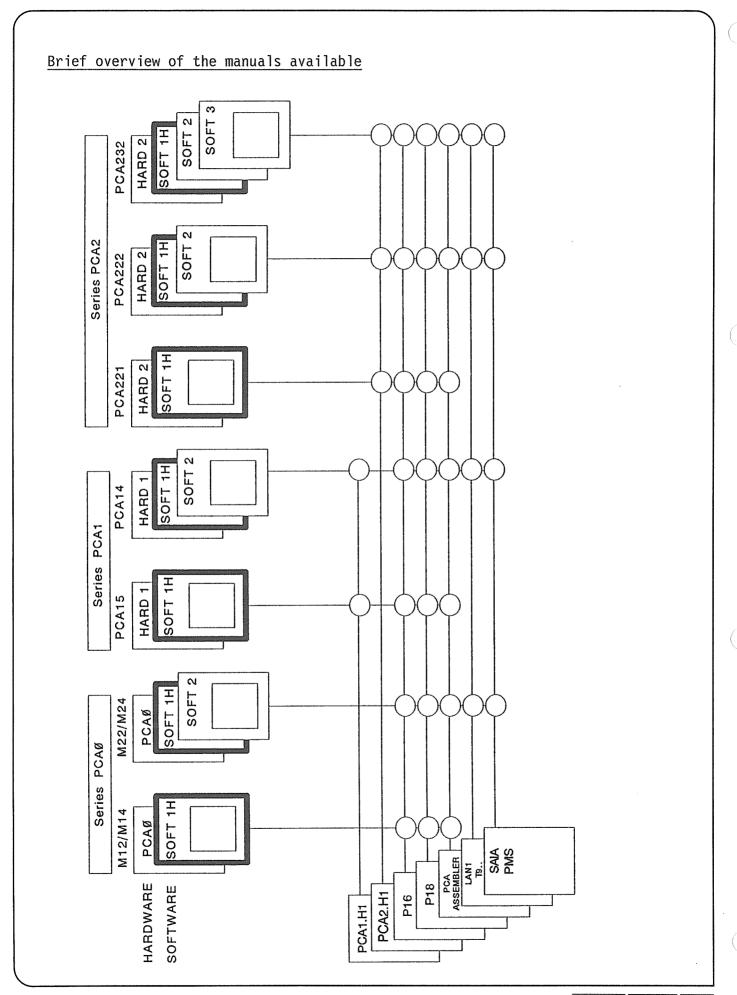

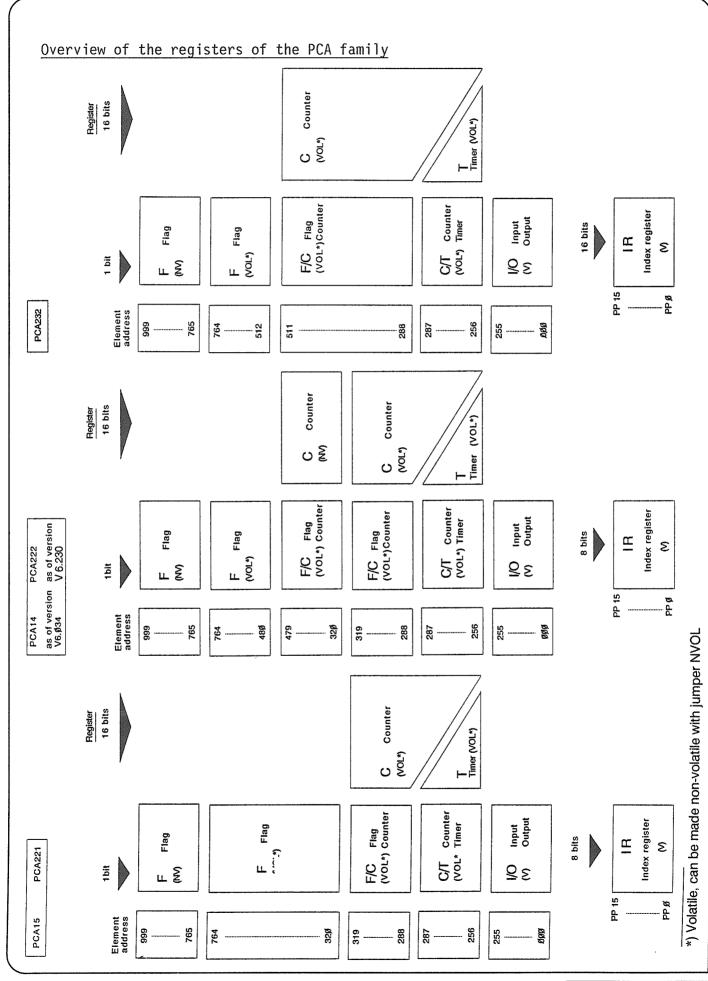

Overview of the SAIA°PLC, system family PCA Brief overview of the manuals available Overview of the registers of the PCA family Basic instructions of the SAIA°PLC, software level 1 Additional instructions of software level 1H

| D 1                                                                | General                                                                                                                                                                                                       |

|--------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D 2                                                                | The program line                                                                                                                                                                                              |

| D 3<br>D 3.1<br>D 3.2                                              | The operands Element addresses Step addresses                                                                                                                                                                 |

| D 4<br>D 4.1<br>D 4.2<br>D 4.3                                     | Further definitions The linkage line The accumulator Normally-open/normally-closed contacts or high/low                                                                                                       |

| D 5<br>D 5.1<br>D 5.2<br>D 5.3<br>D 5.4<br>D 5.5<br>D 5.6<br>D 5.7 | Programming methods Programming by ladder diagram Programming by logic diagram Programming by flowchart Combined programming Programming with parallel programs Programming with subroutines Address indexing |

# Overview of the SAIA°PLC, system family PCA

# System PCA

|                                                                                                                                                                                                               | Series PCAØ                                                                                                   | Series PCA1                                                                                                                           | Series PCA2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Software level 3 Software level 2 + 32 word instructions for - arithmetics, ±9 digits - data transfer - word register                                                                                         |                                                                                                               |                                                                                                                                       | User memory BK program lines + 8K text character + 8K byte data 256 or 512 I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Software level 2 Software level 1H + serial data interface + date-time + data register + parameter instructions (soft- interrupt, FIFO, PID)                                                                  | Standard and OEM-versions PCAG.M22 PCAG.M24 M22                                                               | PCA141 PCA147 PCA147 +C45  PCA141 PCA147 PCA147 +C45                                                                                  | PCA222caecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecaecae |

| Software level 1H 32 basic instructions for  - timer and counter functions  - parallel programs and subroutines  - indexing etc.  20 additional instructions for  - arithmetics  - data transfer  - check-sum | Standard versions PCA@.M12 PCA@.M14  PCA@.M12 PCAG.M14  24/32 I/O 48/64 I/O User memory max. 4K program lines | PCA151 PCA156 PCA157 +C45  PCA151 PCA156 PCA157 +C45 M51M55M57C45  32 (56) 64 (112) 128 (224) I/O  User memory  max. 4K program lines | PCA221c39c39c39c39c39c39c39c39c39c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34c34                                                                                                                                                    |

# Basic instructions of the SAIA°PLC, software level (1H) Instructions of software level (1H)

Step (or line) address Instruction in numerical code

Element or jump address

OPERAND

Accumulators status indicator

STEP

LED display on SAIA PLC programming input unit

|           |                                  | Numerical<br>code | Mnemo-<br>code | Instruction                              | Description                                                                               |

|-----------|----------------------------------|-------------------|----------------|------------------------------------------|-------------------------------------------------------------------------------------------|

|           | Logic Instructions               | Ø1<br>Ø2          | STH<br>STL     | Start High Start Low                     | Start link with interrogation / High of the element according to Low                      |

| 人 .       |                                  | Ø3<br>Ø4          | ANH<br>ANL     | AND High<br>AND Low                      | AND linkage of accu with High following elements interrogated on Low                      |

|           |                                  | Ø5<br>Ø6          | ORH<br>ORL     | OR High OR Low                           | OR linkage of accu with the following element interrogated on Low                         |

|           |                                  | Ø7                | XOR            | Exclusive OR                             | Comparison of two elements                                                                |

| •         |                                  | Ø8                | NEG            | Negate Accu                              | Negate (invert) status of accu                                                            |

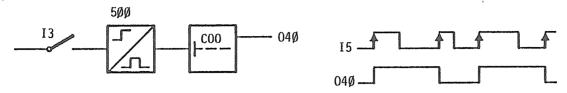

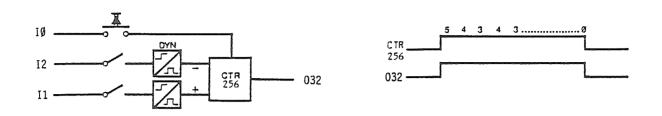

|           |                                  | Ø9<br>            | DYN            | Dynamic Control                          | Dynamic acts so that result of linkage affects accu for first cycle only                  |

|           | Switching Instructions           | 1Ø                | OUT            | Set Output with<br>Status of Accu        | Set output or flag with the status of accu                                                |

|           |                                  | 11<br>12          | SEO<br>REO     | Set Output<br>Reset Output               | Set (latch) output or flag (if accu = 1) Reset (unlatch) output or flag (if accu = 1)     |

|           |                                  | 13                | C00            | Complement<br>Output                     | Interrogate output or flag and set it to the opposite state (if accu = 1)                 |

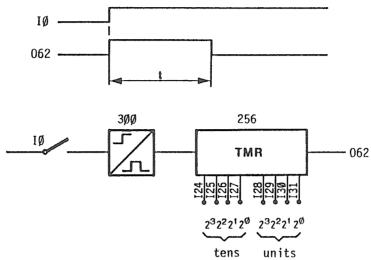

|           | Timing and Counting Instructions | 14*               | STR*           | Set Timer                                | Set timer to determined value and start it running (if accu = 1)                          |

|           |                                  | 15*               | SCR*           | Set Counter                              | Set counter to determined value (if accu = 1)                                             |

|           |                                  | 17<br>18          | INC<br>DEC     | Increment Counter<br>Decrement Counter   |                                                                                           |

|           | Jump Instructions                | 2Ø                | JMP            | Unconditional Jum                        | p Unconditiónal jump to step address                                                      |

|           |                                  | 21<br>22          | JIO<br>JIZ     | Jump if Accu is On<br>Jump if Accu is Ze |                                                                                           |

|           |                                  | 23<br>24          | JMS<br>RET     | Jump to Subrouting<br>Return from Subro  |                                                                                           |

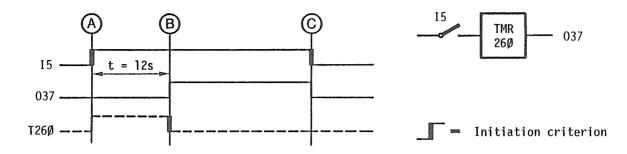

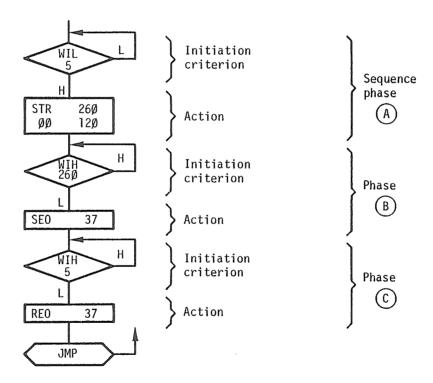

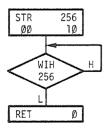

| <b>14</b> | Wait Instructions                | 25<br>26          | WIH<br>WIL     | Wait if High Wait if Low                 | Wait whilst interrogated element is / High                                                |

|           | Auxiliary Instructions           | ØØ                | NOP            | No Operation                             | No operation                                                                              |

|           |                                  | 19                | SEA            | Set Accu                                 | Set accumulator status to 1                                                               |

|           |                                  | 16                | SEI            | Set Index                                | Set index register to operand value                                                       |

|           |                                  | 27<br>28          | INI<br>DEI     | Increment Index<br>Decrement Index       | Increment   1 content of index register by 1   Decrement   f (until to the operand value) |

|           |                                  | 29**              | PAS**          | Program Assignme                         |                                                                                           |

|           |                                  | 3Ø                | DOP            | Display Operand                          | Display content of operand (if $accu = \emptyset$ )                                       |

|           |                                  | 31                | DTC            | Display Timer or<br>Counter              | Display timer or counter value (if accu = 1)                                              |

<sup>\*</sup> Two line instruction (second line contains determined value)

<sup>\*\*</sup> Two line instruction (second line contains starting address of parallel programme)

# Additional instructions of software level 1H

|                                 | Mnemo<br>code | Num.<br>code                                       | Instruction<br>English             | Description                                                                                                                                                                                                                   |

|---------------------------------|---------------|----------------------------------------------------|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Transfer instruc-tions          | STR<br>SCR    | 14<br>15                                           | Set Timer<br>Set Counter           |                                                                                                                                                                                                                               |

|                                 |               | 19<br>20<br>21<br>22<br>23<br>24<br>25<br>26<br>31 | > 2nd line                         | Enter 5 x 4 bits BCD  Output 5 x 4 bits BCD  Output 8 bits binary  Output 12 bits binary  Output 16 bits binary  Enter 8 bits binary  Enter 12 bits binary  Enter 16 bits binary  Transfer counter  or index register counter |

| Arithmetic<br>instruc-<br>tions | SCR           | 15<br>27<br>28<br>29<br>3Ø                         | Set Counter    2nd line            | Add + Subtract - Multiply x Divide :                                                                                                                                                                                          |

| Indexing instruc-               | SEI           | 16                                                 | Set Index                          | Set index register to preselected value                                                                                                                                                                                       |

| tions                           | INI<br>DEI    | 27<br>28                                           | Increment-Index<br>Decrement-Index | Increment } the index re-<br>Decrement } gister by 1                                                                                                                                                                          |

|                                             | Mnemo<br>code | Num.<br>code | Operand | Description                                            |

|---------------------------------------------|---------------|--------------|---------|--------------------------------------------------------|

| Special<br>instruc-                         | PAS           | 29           | 18      | Modification of the number of active parallel programs |

| tions (these<br>are 2-line<br>instructions) | PAS           | 29           | 30 38   | Check sum                                              |

As evident from the previous pages, the instruction set of the entire SAIA°PLC family is <u>completely upwards compatible on 4 levels</u>.

Level  $\bigcirc$ 1, which includes 32 basic instructions, was reserved for the older series PCA13 and PCA210.

The lowest level today is (1H). On this level, 2Ø additional comfortable instructions are made available for series PCAØ, PCA15 and PCA221.

This intelligence level is described in this manual.

It is possible to write simple operating programs with just 5 instructions. In order to make full use of the entire level (H), however, timer and counter functions, parallel programs and subroutines as well as arithmetic functions can be performed.

The higher intelligence levels 2 and 3 of series PCA14, PCA222 and PCA232 comprise all the basic functions, so that programs of level 1H can still be used, should the requirements grow.

#### PART D INTRODUCTION

#### D 1 General

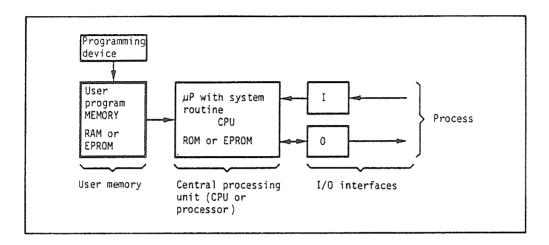

As has already been shown in the hardware introduction, the characteristics of the CPU are determined by the system routine of the  $\mu P$  system. The overall characteristic of the PLC is determined by the system routine. The user has no means of access to the system routine. Individual adaptation to the different process conditions takes place via the user program.

This user program is entered into the user memory in the problem-oriented SAIA°PLC language. It is programmed by means of various available programming devices.

The CPU (also known as the processor) is now capable of "reading" the user program and performing the instructions contained in it, such as e.g. interrogation of input states, their linking and transmission of the result to outputs, thus controlling the process in the desired manner.

According to the task in hand, the program can be prepared as required in accordance with one of the following control descriptions:

- Ladder diagram (circuit diagram)

- Logic diagram (signal flow diagram)

- Flowchart (sequence diagram)

- Function chart in accordance with DIN 44719 or GRAFCET (step control)

The different programming methods may be combined with one another.

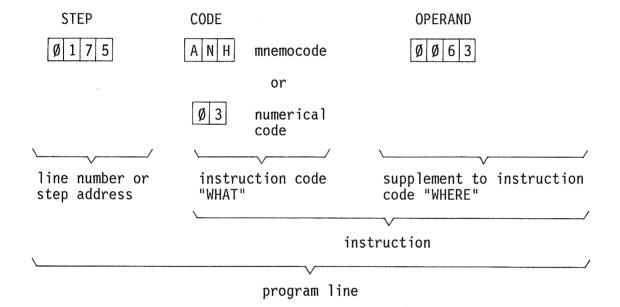

#### D 2 The program line

Each instruction in the user program comprises 1 program line (in certain cases 2 or 10 lines). In addition to the line number or step address (STEP), a line also contains the instruction code (CODE) and the operand (OPERAND). The instruction code states "WHAT" sort of instruction is to be performed, whilst in the operand it is determined "WHERE" this instruction is to take effect.

Each program line comprises 16 bits, so that 1K = 10/24 program lines can be stored in a 16 K bit user memory (e.g. EPROM 2716).

Structure of the program or instruction line:

STEP The location of the instruction in the user memory is defined by the line number. Decimal numbering from  $\emptyset...2\emptyset47$  (2K) or  $4\emptyset95$  (4K).

CODE Depending on the programming unit the <u>instruction code</u> can be entered as a <u>3-character mnemocode</u> or as a <u>numerical code from  $\emptyset$  to 31</u>. The mnemocode is an abbreviation of the English term for the corresponding instruction. Therefore, it can be easily remembered and is internationally understood.

OPERAND Here, by means of jump instructions, the <u>element address</u> (input, output, timer, counter or flag) or the <u>target address</u> (line number) is entered.

Timer and counter instructions comprise 2 program lines. In the second line, the corresponding timer or counter value appears in the operand.

#### D 3 The operands

As has already been mentioned in the previous description, the operands are the so-called element addresses or step addresses (line number).

#### D 3.1 Element addresses

All addressable elements (inputs, outputs, timers, counters, non-retentive and retentive flag memories) are numbered decimally from  $\emptyset...999$ .

- The inputs and outputs in the form of interface modules can be plugged into the basic unit of the PLC. They are addressed either from the installation location (PCAØ and PCA1) or by means of a DIL switch (PCA2).

The address range can be assigned as required, alternatively however, only by means of an input or an output module. (An exception here is the PCA2.C3Ø extension rack, by means of which it is possible to attain 256 I + 256 0 = 512 I + 0).

It is only possible to interrogate the signal states of inputs.

Outputs can be set (switched on) and reset (switched off) and their signal status interrogated (exceptions for certain modules).

- <u>Timers and counters</u> are programmable registers which are located in the <u>CPU module</u>. They can be used alternately as timers or counters.

- Non-retentive and retentive flags are 1 bit storage cells which can be treated like outputs, e.g. they can be set or reset, and interrogated as to their signal state. Accordingly non-retentive and retentive flags are suitable for the storage of any information.

On the hardware side, these are also located in the CPU module in the form of a separate RAM memory. Because this RAM memory is provided with a back-up battery, the 235 retentive flags retain their information - even in the event of a power failure - for in excess of 1 month. Although the 477 non-retentive flags are likewise provided with a battery back-up, they are reset to the "L" signal state when the PLC is switched on. Therefore they act as zero voltage resetting flags.

Insertion of hardware bridge NVOL in the CPU module enables all 712 flags to become retentive, as well as all timers and counters.

#### D 3.2 Step addresses

The second type of operands are the step addresses or line numbers. These are required in connection with jump instructions. In this combination it can be determined to which point in the user program the jump is to be made. In order to cover the entire user memory, all step addresses from  $\emptyset$  to  $2\emptyset47$  can be used as operands.

Due to 2-line jump instructions provided for the more efficient CPUs (from intelligence level (IH) on, the step address range is increased to 8191 (8K).

#### D 4 Further definitions

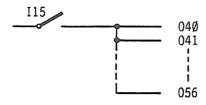

#### D 4.1 The linkage line

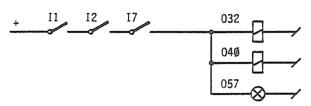

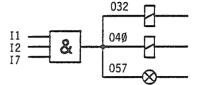

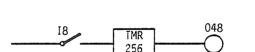

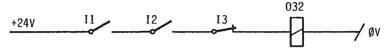

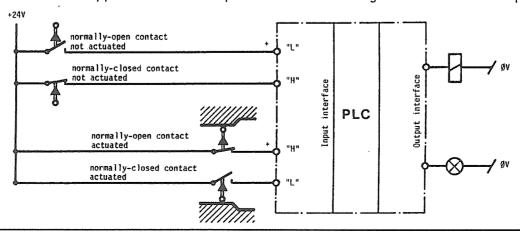

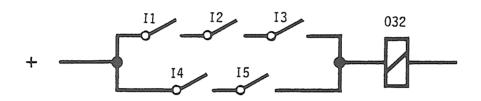

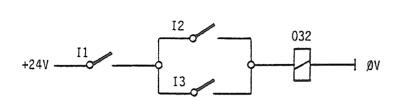

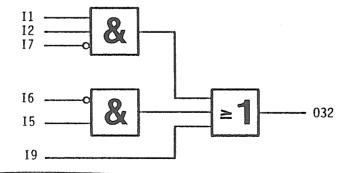

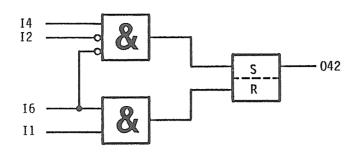

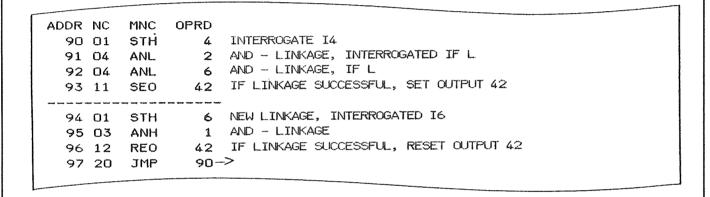

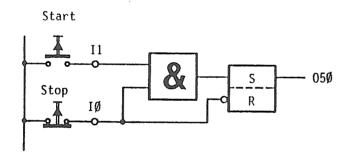

An example using the ladder or logic diagram:

Program

A linkage line is a section of a program and consists of several instruction lines. It is a self-contained linkage of elements. It normally commences with a start instruction (STH or STL). The linkage is considered successful when the end result = 1, e.g. when, in our example outputs 032, 04 $\emptyset$  and 057 are activated (switched on).

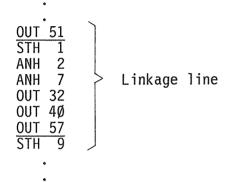

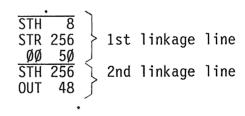

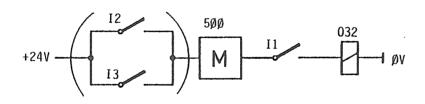

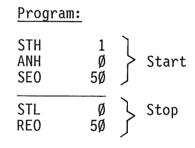

An example with a timer:

Program

As the adjacent program shows, the above function comprises 2 linkage lines. In the first linkage line, input I8 is interrogated and on the basis of its signal state, the timer is set (comparable with a time relay control circuit). In the 2nd linkage line the timer signal state is transferred to output 048 (comparable with a time relay load circuit).

# D 4.2 The accumulator = ACCU

This memory is also located in the CPU and consists of a single storage position which can assume the logical status  $\emptyset$  or 1.

In order to process a complete linkage as far as an action instruction, the existing intermediate result of the linkage must be stored in the ACCU. At the end of a linkage the end result is present in the ACCU ( $\emptyset$  or 1). On the basis of this result the corresponding element (e.g. an output) is either not activated (ACCU =  $\emptyset$ ) or activated (ACCU = 1).

By means of the result stored in the ACCU following instructions can also be skipped (e.g. see jump instructions).

#### D 4.3 Normally-open/normally-closed contacts or high/low

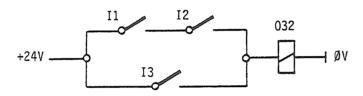

A contact linkage as shown in the schematic diagram below is wired exactly in accordance with the schematic diagram:

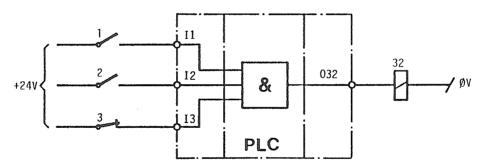

If this problem is solved with a PLC, then each contact is led to an input. Linkage then takes place in the PLC processor and not by means of wiring. The above linkage suitable for a PLC is shown in the figure below:

A PLC cannot determine whether normally-open or normally-closed contacts are connected to its inputs. It does however determine whether a high signal (H) or a low signal (L) is applied to the input. These signal levels are accurately defined in the hardware section for each input interface. For a 24V input in source mode (normal case), it can be stated as a simplification that:

- where +24V is applied to the input -----> signal state "H" is produced - where  $\emptyset$ V is applied to the input ----> signal state "L" is produced

However the widely used method of representation using contact symbols can be used for programming the PLC as long as the following rules are observed. The following applies to source mode, e.g. with the contact at +24V:

- If a contact in its closed state assists a successful linkage, then the contact concerned must be interrogated if high or linked (normal case).

- If a contact in its open state assists a successful linkage, then the contact concerned must be interrogated if low or linked.

In addition to mechanical contacts these same considerations also apply to proximity switches and light barriers.

For the sake of uniformity it is standard practice to employ only normally open contacts. This is indeed correct for approximately 90% of the cases. With some special applications, however, the use of normally closed contacts is unavoidable for safety reasons. As a simplification it can be stated:

- A procedure must always be started by means of "apply voltage", while it is always stopped by switching off the supply.

In order to take these prior considerations into account, the interrogation and linkage instructions are always in pairs:

| STH   | STL   |

|-------|-------|

| ANH   | ANL   |

| ORH   | ORL   |

| (WIH) | (WIL) |

| (JIO) | (JIZ) |

"H":

This means that the input signals can in each case be interrogated if "H" or "L". Where the type of interrogation is in agreement with the actual signal status at the input, this is then processed as a logical "1" in the ACCU.

Signal states do not just apply to inputs but to all addressable elements:

```

Inputs

+24V applied (standard, source mode)

"L":

ØV applied (standard, source mode)

"H":

Outputs

output set = transistor on-state

"| ":

output not set = transistor blocked

"H":

Non-retentive/

set

" :

retentive flags

not set or reset

"H":

Timers

timer has been set and runs

"L":

timer has not been set or has run down

"H":

Counters

counter has been set and register content > \emptyset

"L":

counter has been not set or register content = \emptyset

```

## D 5 Programming methods

A programmable control provides a high degree of flexibility concerning the design and adaptation of the program. However as with traditional controls, the PLC does not take the control designer's responsibility of producing a clear description of the control task beforehand. According to type of process and the preference of the designer, this description is produced in the following manner.

Because the SAIA°PLC instructions set is so versatile, the most diverse control descriptions are suitable for use as models for a PLC program.

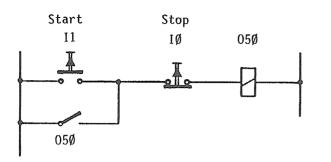

#### D 5.1 Programming by ladder diagram

#### Model:

# Program (instruction list):

#### Characteristics:

- ----> Instructions required STH, STL, ANH, ANL, ORH, ORL, OUT.

- The linkage is shown by contact symbols. The outputs receive the results of the prior AND/OR linkages.

- All program parts circulate in a cyclic fashion. This is termed a pure circulating program because it contains no wait and no conditional jump instructions.

#### Advantages:

- Simple program preparation with only 7 instructions for users of ladder diagrams.

- Well suited to monitoring tasks.

- Different linkage lines can be strung together almost as desired.

#### Disadvantages:

- Less suitable for sequential processes (sequence controls), because all parts which are inactive at a given time must be interlocked.

- Mor complex controls become extremely complicated in the ladder diagram form.

- Restricted instruction set.

- In the case of large programs a long reaction time.

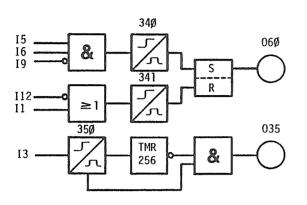

#### D 5.2 Programming by logic diagram

#### Model:

# Program (instruction list):

# Characteristics:

- ----> Additional available instructions SEO, REO, COO, STR, SCR, NEG, DYN etc.

- The linkage is shown with function oriented logic symbols enabling the signal flow to be followed up in a similar fashion to the ladder diagram.

- All program parts circulate in a cyclic fashion (pure circulating program).

#### Advantages:

- The outputs can be set accumulating or non-accumulating.

- Well suited for monitoring tasks and pure logic programs.

- Since a large part of the instructions set can be used, even more complex problems are easily realizable.

- Different linkage lines can be strung together almost as desired.

#### Disadvantages:

- Less suitable for sequential processes (sequence controls), because all parts which are inactive at a given time must be interlocked.

- In the case of large programs a long reaction time.

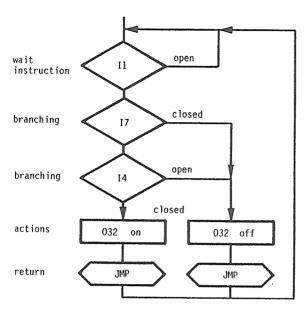

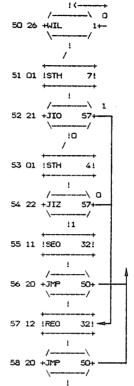

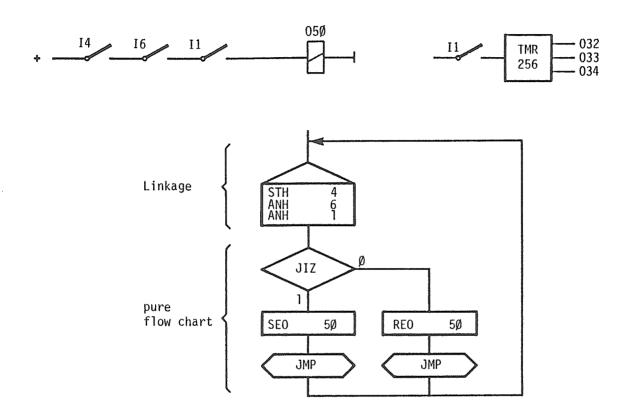

# D 5.3 Programming by flowchart

#### Model:

#### Program in flowchart form:

#### Program in instruction list form:

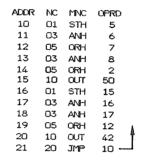

|          | ADDR            | NC  | MNC  | OPRD |

|----------|-----------------|-----|------|------|

|          | 50              | 26  | WIL. | 1.   |

|          | 51              | 01  | STH  | フ    |

|          | <b>一</b> 52     | 21  | JIO  | 57   |

|          | 53              | 01  | STH  | 4    |

|          | <del> </del> 54 | 22  | JIZ  | 57   |

|          | 55              | 1.1 | SEO  | 32   |

| $\vdash$ | <u> 56</u>      | 20  | JMP  | 50   |

|          | <b>-</b> 57     | 12  | REO  | 32   |

| L        | <del></del> 58  | 20  | JMP  | 50   |

# **Characteristics:**

- ----> Special instructions WIH, WIL, JIO, JIZ

- Wait loops can be formed; these can be retained by the processor until the conditions for continuation are fulfilled.

- Branchings with conditional jump instructions are possible.

- This programming method is suitable for sequential processes (sequence controls).

#### Advantages:

- Simple programming, in accordance with the functions in the sequential process.

- This programming method is easily understood by the process engineers.

- Due to the wait loops, the program runs only as fast as the process itself. This results in simple commissioning and rapid trouble-shooting.

- Very short reaction times. They are very often determined only by the delay of the input interface.

#### Disadvantages:

- Monitoring functions must be incorporated in separate parallel programs.

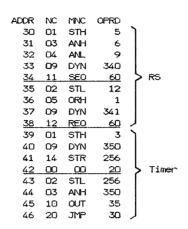

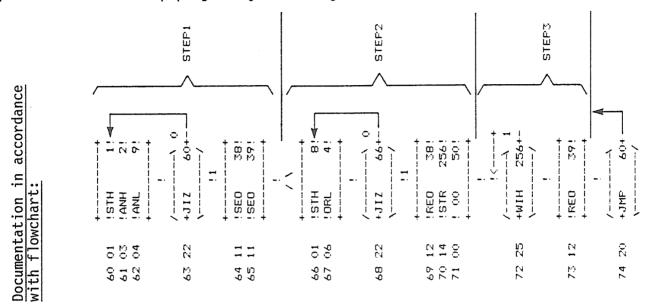

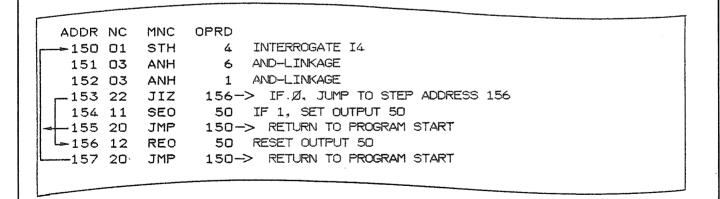

# D 5.4 Combined programming by flowchart / logic or in accordance with Grafcet

The universal program language of the SAIA°PLC permits the preparation of a practice related step program by combining instructions.

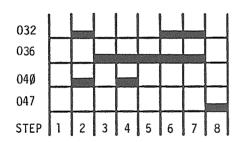

step ] step 2 step 3 Model in accordance with dool dool dool action noitos condition condition 1 LEW conditional conditiona Flowchart Explanation return Flowchart: 38 256 50 in accordance with 00 of 1 5s function chart: 038 33 033 003 039 112 **T256**  $\sim$ Mode 1

Features: Flexibility is further enhanced owing to the use of logic instructions.

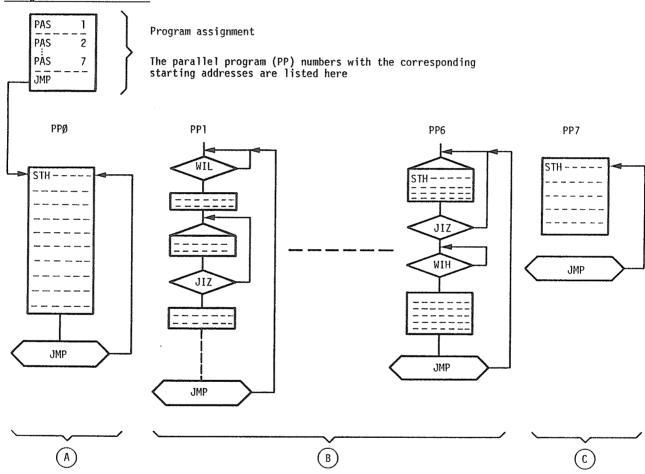

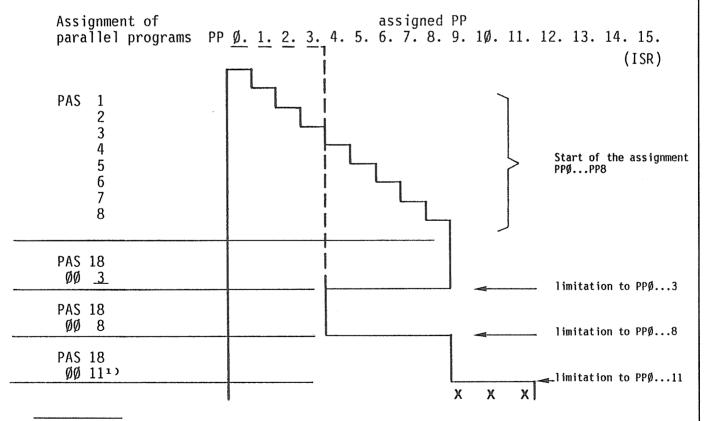

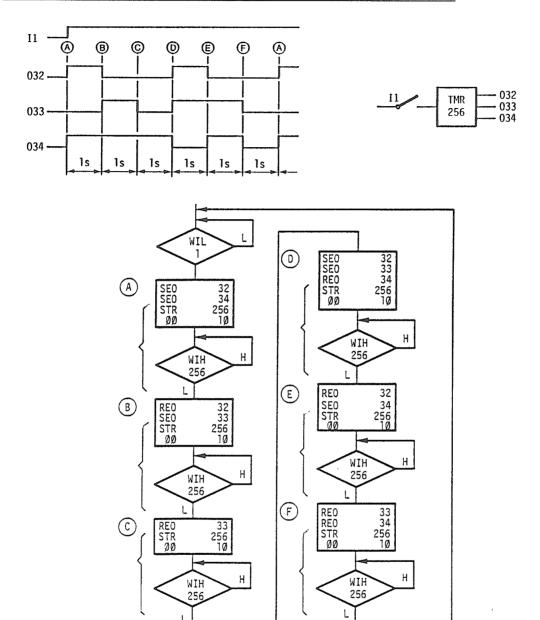

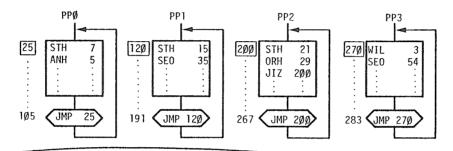

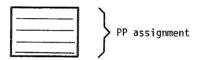

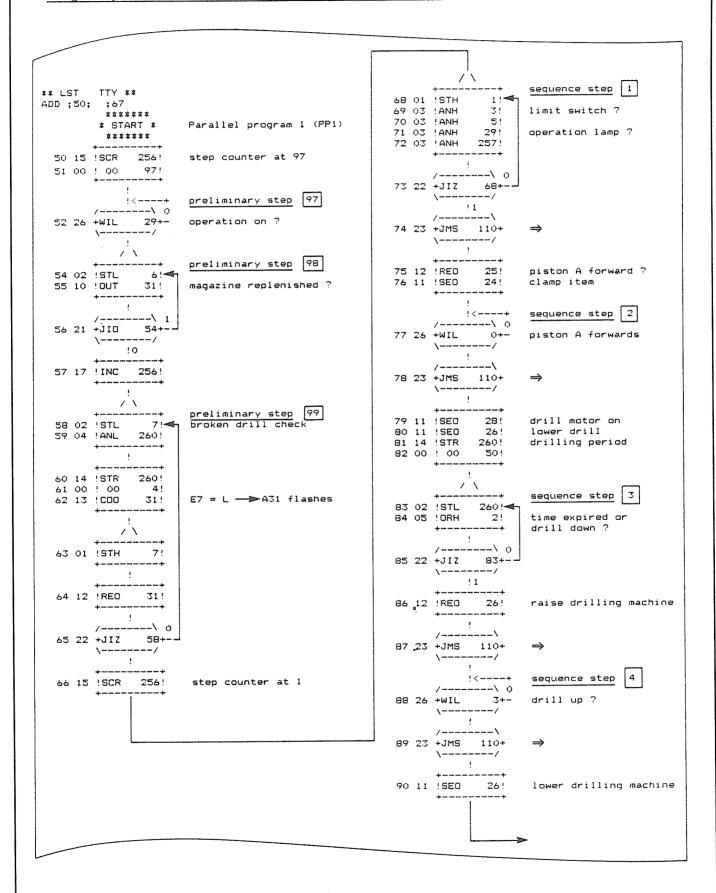

## D 5.5 Programming with parallel programs

Optimal conditions are attained with the use of parallel programs. Up to 16 parallel programs can be employed which are independent of one another and which run asynchronously. This means that different sequential functions of a machine (e.g. an automatic assembly machine) can be accommodated in different programs in accordance with the sequence plan and run step by step with the advance of the process.

Monitoring and continuously active functions are accommodated in a parallel circulating program.

#### Program structure:

- (A): PPØ (parallel program Ø) is a pure circulating program (without wait loops) with monitoring and continuously active functions.

- B: PP1 to (e.g.) PP6 are parallel sequence programs in the flowchart of different asynchronously circulating sequential functions.

- ©: PP7 is a brief, pure circulating program which contains a few functions requiring extremely short reaction times.

#### Characteristics:

----> Instruction PAS for program assignment.

See program structure for other characteristics.

#### Advantages:

- Sequential runs (with wait loops) and continuously active functions (monitoring, pure logic etc.) can be separately programmed in the most suitable way.

- Only that number of parallel programs are assigned as are required (max. 16).

- By means of appropriate software-interrupt facilities sequential programs can be stopped or started from the beginning at any time (PAS 18 instruction).

#### Disadvantages:

- In order to maintain rapid reaction times for continuously active functions, it is advantageous to process these in a separate short circulating program.

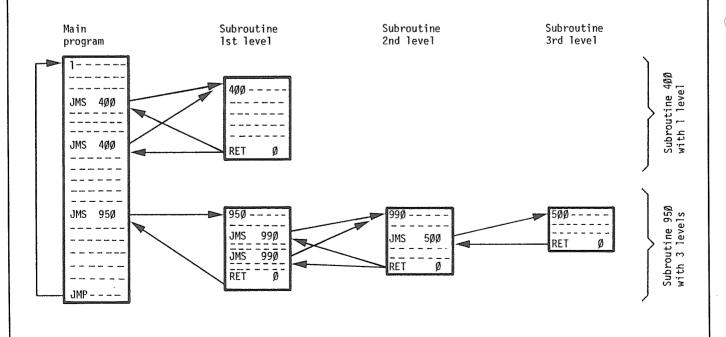

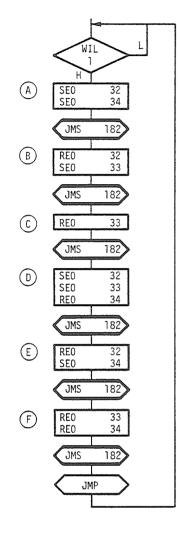

#### D 5.6 Programming with subroutines

----> Instructions required JMS and RET.

Frequently repeated parts of programs may be entered as subroutines.

Subroutines can be used in all the previously described program techniques, e.g. ladder diagram, logic diagram, flowchart or when using parallel programs.

Subroutines save memory capacity and programming time. Also, by using subroutines, programs are clearly subdivided into functional blocks (structured programming).

As many subroutines as desired can be activated, each subroutine available in up to three levels. It is only necessary to ensure that a jump is not made simultaneously into the same subroutines from different PPs.

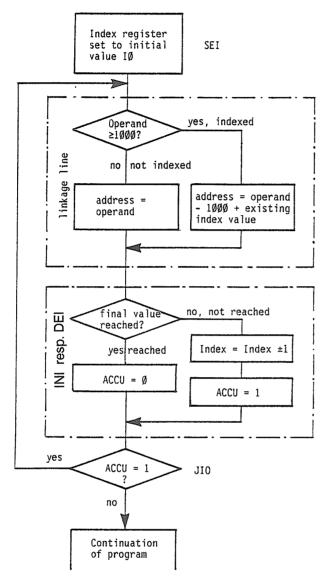

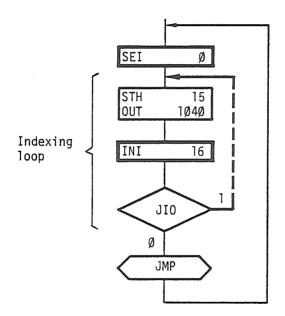

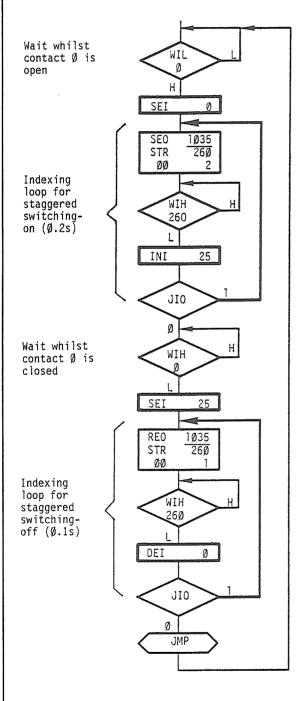

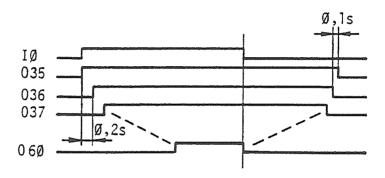

# D 5.7 Address indexing (series processing)

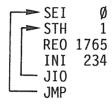

----> Instructions SEI, INI, DEI

Whenever several elements (inputs, outputs, flags or timers) have to be processed in the same fashion (e.g. in monitoring circuits or with shift registers), the result is normally long programs of low linkage depth. If for instance, all 235 retentive flags are to be reset by pressing a pushbutton, 236 program lines would be required. By using address indexing the same task can be programmed with only 5 program lines.

#### Without indexing:

| REO | 1   |

|-----|-----|

| REO | 765 |

| REO | 766 |

| REO | 767 |

| REO | 768 |

| REO | 769 |

| REO | 77Ø |

| REO |     |

| REO | 997 |

| REO | 998 |

| JMP | 999 |

#### With indexing:

The indexing loop will run through 1 + 234 times, the element address (provided with 1000) being increased by 1 each time.

| Note | s: |  |  |

|------|----|--|--|

|      |    |  |  |

|      |    |  |  |

|      |    |  |  |

|      |    |  |  |

|      |    |  |  |

|      |    |  |  |

|      |    |  |  |

|      |    |  |  |

NOP

No operation

NOP: No Operation ---> no operation

Instruction format:

| Instruct      | Operand           |   |

|---------------|-------------------|---|

| Mnemo<br>code | Numerical<br>code |   |

| NOP           | ØØ .              | Ø |

Although this instruction is processed by the processor, no functions are initiated. Its purpose is to create spare places for additions to the program and to fill gaps in the program.

Program lines which become superfluous after an alteration can be overwritten (cleared) with NOP. Successive NOPs are obtained by the multiple actuation of the "Enter" pushbutton on the programming unit.

SEA

Set ACCU = 1

SEA: Set Accumulator = 1 ---> ACCU is set to 1

Instruction format:

| Instruct      | Operand           |   |

|---------------|-------------------|---|

| Mnemo<br>code | Numerical<br>code |   |

| SEA           | 19                | Ø |

The ACCU is set unconditionally to 1 with SEA. Therefore SEA is used before instructions which are only performed when ACCU = 1, e.g. before DTC.

Part F Example 8

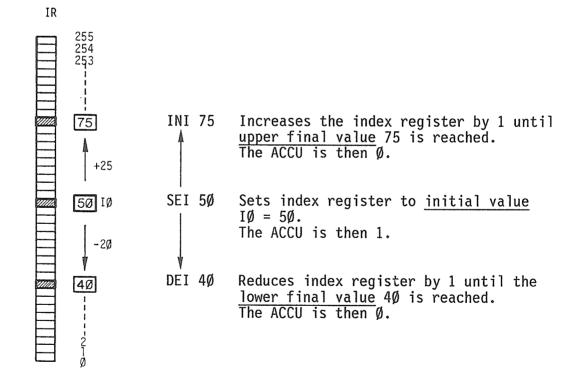

#### E 6 Indexing

SEI INI DEI

Element addresses - indexing (series processing)

SEI: Set Index ---> set the index register to the <u>initial value</u> in accordance with operand

INI: Increment Index ---> increase index register by 1 up to the upper

final value in accordance with operand

<u>DEI:</u> Decrement Index ---> reduce index register by 1 down to the <u>lower</u> final value in accordance with operand

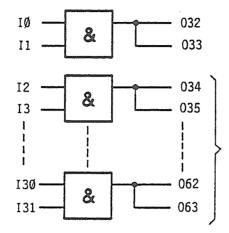

It is frequently necessary for series of inputs, outputs, flags, timers or counters must be treated in the same way (for example resetting of all retentive flags in accordance with D 5.7). In cases like this, long and time-consuming programs can be drastically shortened with the help of address indexing.

This is facilitated by the index register IR, which is a type of counter register having a capacity from  $\emptyset$  to 255\*. In three instructions enable the register content to be set or altered to the desired limiting value.

#### Example:

The CPU of PCA232 has index registers with a capacity of 1K  $(\emptyset...1\emptyset23)$  (see example d) at the end of this chapter).

<sup>\*)</sup> Each parallel program has its own index register, providing a total of 16. These registers lose their contents in the event of a power failure.

All element operands which are shown in the description in Part E with (i) can be indexed. The processor adds the existing reading of the index register to the element address shown in the operand.

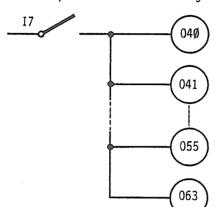

An example should clarify this:

By activation of I7, outputs  $04\emptyset$  to 055 and additionally output 063 are to be activated.

The index register is set to initial value  $\emptyset$ .

SEI Ø

STH 7

OUT 1040

OUT 63

INI 15

Interrogation of input I7.

Indexing is initiated after output 040 by addition of the <u>number 1000</u>. In the first loop run, address 040 is not altered because the index register is first of all 0 (SEI 0). With the following runs the register content is each time increased by 1 by means of the instruction INI, so that outputs 041, 42, 43 to 55 are set one after the other.

Output 063 is directly addressed (without 1000), so the index register has no effect on this.

INI effects the increase of the register by 1 per run up to the value 15. As long as the register is <15, the ACCU has the value 1 after processing INI 15.

Therefore the conditional jump is performed until the loop is executed  $\emptyset$  to 15 times, e.g. 16 times, and all 16 outputs from 04 $\emptyset$  to 055 have been processed.

Part F

Examples: 15, 16, 17

#### Second example:

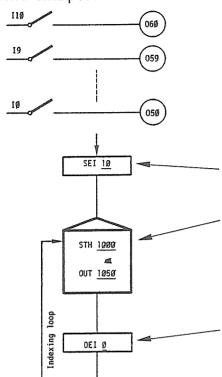

Inputs I10 to I0 are to activate outputs 060 to 050. The action is to take place in descending order by means of DEI.

The index register is set to the initial value 10 (10 - 0 = 10 or 60 - 50).

Both inputs and outputs are to be indexed; this taking place by the addition of 1000. The lowest addresses in the series are entered since initially the register content 10 is added. Therefore, firstly 110 is activated with 000, then 100 with 0000.

DEI causes the register value to be reduced by 1 for each run, until the given value  $\emptyset$  is reached.

When register value  $\emptyset$  = DEI  $\emptyset$  the ACCU is likewise  $\emptyset$ , so the indexing loop is now vacated.

#### Instruction formats:

| Instructi     | on code           | Operand Operand                                     |                    |  |

|---------------|-------------------|-----------------------------------------------------|--------------------|--|

| Mnemo<br>code | Numerical<br>code | Description                                         | Range              |  |

| SEI           | 16                | Initial value<br>(IØ) of the in-<br>dex register    | IØ = Ø255          |  |

| INI           | 27                | Upper final value<br>for incrementing<br>indexation | 1255 1)            |  |

| DEI           | 28                | Lower final value<br>for decrementing<br>indexation | Ø254 <sup>2)</sup> |  |

- 1) By applying INI, the next index register value after 255 is Ø Ø (...254, 255, Ø, 1...)

- By applying DEI, the next index register value after Ø is 255 (...1, Ø, 255, 254).

#### Truth table:

| Instruction | Effect on ACCU                                                                 |

|-------------|--------------------------------------------------------------------------------|

| SEI         | Instruction sets ACCU = 1                                                      |

| INI         | If register value ≠ operand> ACCU = 1<br>If register value = operand> ACCU = Ø |

| DEI         | If register value ≠ operand> ACCU = 1<br>If register value = operand> ACCU = Ø |

#### Summary of indexing

#### Indexing scheme:

#### a) Indexing with INI

- Register generally set to  $\underline{\text{value}}$   $\emptyset$  with SEI.

- The <u>lowest addresses</u> (+1000) of the elements to be indexed are used.

- The upper final value for INI is obtained from the <u>difference</u> between highest and lowest address which are to be indexed.

# b) Indexing with DEI

- Register generally set to <u>value</u> X with SEI.

X = <u>difference</u> between highest and lowest addresses which are to be indexed.

- The <u>lowest addresses</u> (+1000) of the elements to be indexed are used.

- Generally  $\emptyset$  is used for the <u>lower final value</u> for DEI.

# Further programming facilities offered using indexing

This section only deals with indexing used for series processing. It is also possible however for the index register to be used so that e.g. subroutines act on other elements according to the status of the index register.

#### Example:

Closing I1 causes 045 to flash, closing I2 causes 050 to flash

#### Main program

| *              | **** | **** | **** | ***** | MAIN            | FROGRAM |

|----------------|------|------|------|-------|-----------------|---------|

| A              | DDR  | NC   | MNC  | OPRD  |                 |         |

| _ <del>-</del> | 700  | 01   | STH  | 1     |                 |         |

| l '            | 701  | 22   | JIZ  | 704   | <del>&gt;</del> |         |

| 11 '           | 702  | 16   | SEI  | 0     |                 |         |

| 11:            | 703  | 23   | JMS  | 710   | $\Rightarrow$   |         |

| Lee-           | 704  | 01   | STH  | 2     |                 |         |

| ,              | 705  | 04   | ANL  | 1     |                 |         |

| <b></b> `      | 706  | 22   | JIZ  | 700   | $\rightarrow$   |         |

| ١ ٠            | 707  | 16   | SEI  | 5     |                 |         |

| i ·            | 708  | 23   | JMS  | 710   | $\Rightarrow$   |         |

| L `            | 709  | 20   | JMP  | 700   | >               |         |

|                |      |      |      |       |                 |         |

#### Subroutine

| SUBROUTINE      | ==== |     |    | ===== |  |

|-----------------|------|-----|----|-------|--|

|                 | OPRD | MNC | NC | ADDR  |  |

|                 | 256  | STL | 02 | 710   |  |

|                 | 256  | STR | 14 | 711   |  |

|                 | 3    | 00  | 00 | 712   |  |

|                 | 1045 | COO | 13 | 713   |  |

| <del>&gt;</del> | 0    | RET | 24 | 714   |  |

|                 |      |     |    |       |  |

|                 |      |     |    |       |  |

|                 |      |     |    |       |  |

|                 |      |     |    |       |  |

# SEI, INI, DEI | Additional functions

SEI(16) iii Setting the index register

- a) iii =  $\emptyset$ ...255 The index register is set to value iii of the operand.

- b) iii = 256...319\* (for PCA232: 256...511) The index register is loaded by the contents of the addressed T/C = iii.

- INI(27) iii Incrementing index register by 1 DEI(28) iii Decrementing index register by 1

- a) iii =  $\emptyset$ ...255 The index register is incremented or decremented as far as the given numerical value iii of the operand.

- b) iii =  $\underline{256...319}$ \* (for PCA232: 256...511) The given value is located in the register of the addressed T/C = iii.

Please note: - All PLCs have 16 index registers, one for each parallel program.

- The counting capacity of these registers is limited to 255. If counter contents are to be transferred to the index register, it should not exceed 255. The maximum capacity of the IR of PCA232 is 10/23 (see example d).

#### General examples:

- a) C267 = 102 Following instruction SEI(16) 267 the index register contents will be 102 as well.

- b) C256 = 44

Following instruction INI(27) 256 the increment limit value will be 44 as well.

- c)  $C26\emptyset = 10\emptyset$ , IR = 4 Following instruction SEI(16) 1256 the index register value will be  $10\emptyset$  (double indexing).

- d) If you need to load values higher than 255, you have to load a counter first.

Example: SCR 28 $\emptyset$  The value 8 $\emptyset$  $\emptyset$  is  $\emptyset$  $\emptyset$  8 $\emptyset$  $\emptyset$  loaded into the SEI 28 $\emptyset$  index register

<sup>\*)</sup> The operand range of counters depends on the hardware and firmware in use (see overview on page III).

#### E 7 PAS-instructions

PAS Ø ... PAS 15 Assignment of parallel programs (PP)

$\underline{\mathtt{PAS:}}$  Program Assignment ---> assignment of the parallel program

Instruction format (two-line instruction):

| Instruction code |                   | Operand                                  |       |

|------------------|-------------------|------------------------------------------|-------|

| Mnemo<br>code    | Numerical<br>code | Description                              | Range |

| PAS              | 29                | Program number,<br>consecutively<br>from | Ø15   |

|                  | ØØ                | Program start<br>address                 | Ø819Ø |

1st line

2nd line

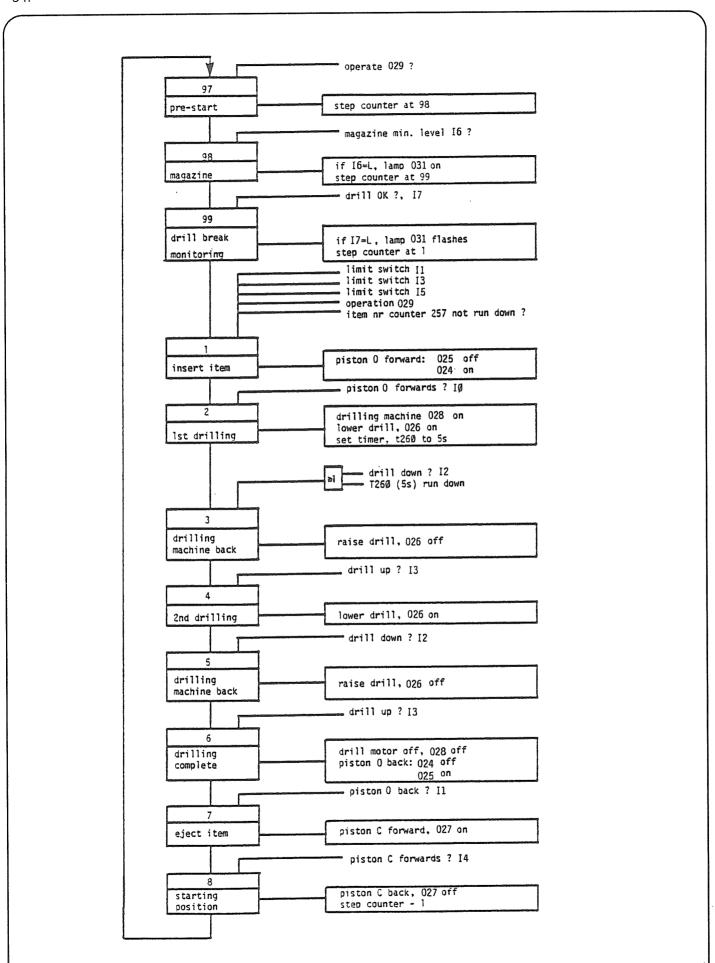

Where several programs run in parallel (maximum 16), then this information must be passed to the CPU right at the program start point. This is done by the assignment of the start addresses of all parallel programs which are to be processed, with the two-line instruction PAS.

The listing of the parallel programs in the assignment part must be continuous (with no numbers left out) from program number 1 in ascending order. The assignment part may usually only be run through once, immediately after switching on the PLC.

PPs may also be "reassigned" with the instruction PAS  $\emptyset...15$ . It is possible, for example, to reassign PP3 from start address 300 to start address 400 in any programm section.

Parallel program  $\emptyset$  does not have to be assigned. It is activated directly after assigning all parallel programs.

Chapter D 5.5 gives details of the PP design and structure. Processing of the individual PP is performed using the "Time Sharing" method. The processor changes from one PP to the next in accordance with precisely defined conditions.

#### Conditions causing a PP change

The following instructions cause a PP change:

- WIH, WIL (if the wait condition is fulfilled)

- JMP, JIO, JIZ, JMS, RET

- and every second or third STH or STL instruction

PAS Ø...15 is always executed irrespective of the ACCU status and does not alter the ACCU status.

Part F

Examples: 13, 18

# PAS 18 Limitation of the assigned parallel programs

All SAIA°PLC allow assignment of up to 16 parallel programs (PP) and running them in parallel. Up to now it has been necessary to reassign a PP to a dummy program loop if it was no longer required. However, no time could thus be saved during the execution of the remaining PPs.

However, it is now possible to limit a maximum number of active PPs with the PAS 18 instruction. After the PP assignment with PAS  $\emptyset$ ...max. 15 a limited number of PPs can be determined from a higher to a lower value in the user program at any place and as many times as desired.

| Instruction code |                   | Operand                  |       |

|------------------|-------------------|--------------------------|-------|

| Mnemo<br>code    | Numerical<br>code | Description              | Range |

| PAS              | 29                |                          | 18    |

|                  | ØØ                | Upper limit<br>of the PP | PP115 |

1st line

2nd line

The PAS 18 instruction is always executed (irrespective of the ACCU status) and does not alter the ACCU status.

<sup>1)</sup> If a higher number than the PPs originally assigned is entered with PAS 18, no malfunction is caused. The inactive PPs 9...11, however, will require processing time in the system program.

PAS 30 PAS 31...38\*

"Check sum" of the system and user program

The "Check sum" function serves to establish the sum to check of the memory contents of the system program (PAS  $3\emptyset$ ) or user program (PAS 31...38). Thus, it can be ensured that the contents of the memories have not been changed.

After execution of the instruction:

ACCU = 1 if the reference value complies with the sum to check,  $ACCU = \emptyset$  if the reference value does not comply with the sum to check.

The instructions PAS 30...38 are always executed irrespective of the ACCU. If a change in memory contents has occurred, the user can take the measures which seem necessary to him: triggering an alarm, resetting the watchdog etc.

#### Check sum of the system program

| Mnemo<br>code | Numerical<br>code | Operand   |

|---------------|-------------------|-----------|

| PAS           | 29                | Always 3Ø |

|               | ØØ                | Always Ø  |

1st line

2nd line

# Check sum of the user program

| Instruction code |                   | Operand Operand            |       |

|------------------|-------------------|----------------------------|-------|

| Mnemo<br>code    | Numerical<br>code | Description                | Range |

| PAS              | 29                | Program<br>part<br>1.K8.K* | 3138* |

|                  | XX                | Reference value            | xxxx  |

1st line

2nd line

The appropriate reference value for the sum to check of the user program is obtained by executing the respective PAS instruction in the operating mode STEP. The PCA displays this reference value on the programming unit for a few seconds. In the operating mode PROG, the corresponding reference value can then be introduced in the 2nd line.

Attention: execution of these instructions takes quite a long time: PAS  $3\emptyset \approx 28.\emptyset$ ms, PAS  $31...38 \approx 8.3$ ms (PCA232: PAS  $3\emptyset \approx 13.6$ ms, PAS  $31...38 \approx 9.5$ ms)

Therefore, use "Check sum" only if the sequence to be controlled allows it, e.g. when switching on the PLC, at the end of an operation cycle, etc.

<sup>\*)</sup> The check-sum of the user program is determined individually for every "K" program (see example on the following page).

It is recommended not to introduce this instruction into the user program until it has been completely developed and tested. Each program alteration, irrespective of whether the program was extended or reduced, causes alteration of the check sum and requires modification of the reference value.

Example: A 2K-user program must be executed upon switching on.

| 20    | PAS        | 31       | "Check sum"  1. K  "Check sum"  2. K      |

|-------|------------|----------|-------------------------------------------|

| 21    | Ø9         | 825      |                                           |

| 22    | JIZ        | 35       |                                           |

| 23    | PAS        | 32       |                                           |

| 24    | Ø7         | 154Ø     |                                           |

| 25    | JIZ        | 35       |                                           |

| 3Ø    | C00        | 255      | Main program with WD-monitoring           |

| 31    | JMP        | 3Ø       |                                           |

| 35 36 | SEO<br>JMP | 15<br>35 | Set alarm output outside the main program |

### Procedure:

- After program input and test, select operating mode STEP

- Key in A 23 +

- -> the reference value for the 2nd K (PAS 32) appears for approx. 20s

- Input of the reference value in operating mode PROG:

A 24 ref. value +

- Same procedure for PAS 31

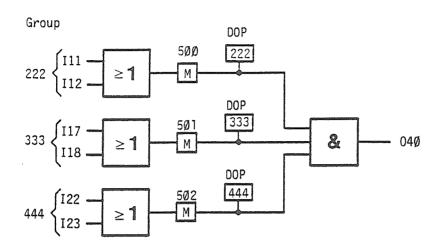

### E 8 Display instructions

D<sub>0</sub>P

Display of an operand

DOP: Display Operand ---> display of the number in the operand

### Instruction format:

| Instruction   | on code           | Operano                                 |       |

|---------------|-------------------|-----------------------------------------|-------|

| Mnemo<br>code | Numerical<br>code | Description                             | Range |

| DOP           | 3Ø                | Whatever num-<br>ber to be<br>displayed | Ø2Ø47 |

DOP is an auxiliary instruction mainly used for commissioning and troubleshooting. A program can be written in such a way that when a particular process situation or a fault occurs, an identification number is displayed. This display is provided in "RUN" mode and is in the operand display of the programming unit or an operand display.

The display is maintained for 1s. If it is required for the display to be maintained for a longer period, the instruction DOP is to be processed at least once per second (mainly in a circulating program). DOP is only performed when a linkage was <u>not</u> successful (ACCU =  $\emptyset$ ).

Part F Example 14

DTC

## Display of a timer or counter reading

DTC: Display Timer or Counter ---> display of timer or counter value

Instruction format:

| Instructio    | n code            | Operano                        | d             |

|---------------|-------------------|--------------------------------|---------------|

| Mnemo<br>code | Numerical<br>code | Description                    | Range         |

| DTC           | 31                | Timer or<br>counter<br>address | 256 319 * (i) |

(i) = indexable

DTC is likewise a valuable auxiliary instruction for commissioning and trouble-shooting.

By means of DTC the timing of a timer or reading of a counter can be displayed on the programming unit or the operand display of the PCA in RUN mode (maximum display 9999).

The display is maintained for 1s. If it is required for the display to be maintained for a longer period, the instruction DTC must be processed at least once per second (mainly in a circulating program). DTC is only performed when ACCU = 1.

Part F

Examples: 8, 18

<sup>\*)</sup> Register structure see page III.

| PARIF   |                                           | PROGRAMMING EXAMPLES                                                                                                                                                                                                                                                                                                                                |

|---------|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Example | 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9 | AND/OR linkage with ladder diagram AND/OR linkage with logic diagram EXOR linkages Linkages with function chart START/STOP circuit with self-holding Pulse divider (stepping switch) Off delay Increment/decrement counter Timer fleeting-on delay with external timing entry in BCD code Switch-on delay with flowchart AND linkage with flowchart |

|         | 12                                        | Sequence control with and without subroutine                                                                                                                                                                                                                                                                                                        |

|         | 13                                        | Operation with parallel programs                                                                                                                                                                                                                                                                                                                    |

|         | 14                                        | Monitoring circuit with fault display on programming unit                                                                                                                                                                                                                                                                                           |

|         | 15                                        | İndexing                                                                                                                                                                                                                                                                                                                                            |

|         | 16                                        | Successive switching                                                                                                                                                                                                                                                                                                                                |

|         | 17                                        | Small monitoring circuit                                                                                                                                                                                                                                                                                                                            |

|         | 18                                        | Circulating program switch                                                                                                                                                                                                                                                                                                                          |

|         |                                           |                                                                                                                                                                                                                                                                                                                                                     |

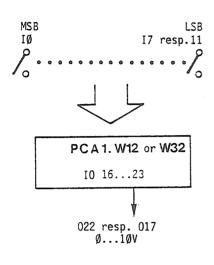

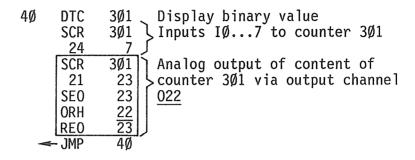

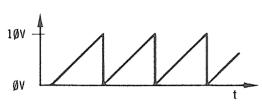

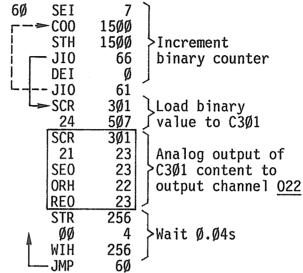

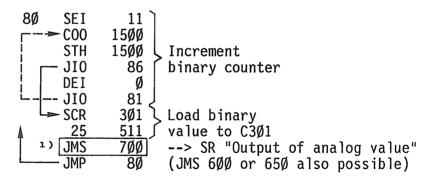

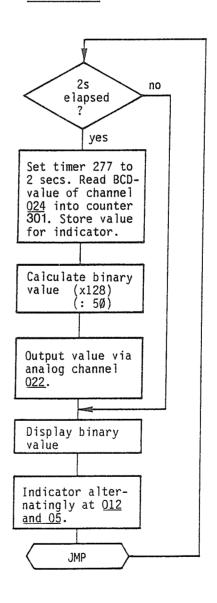

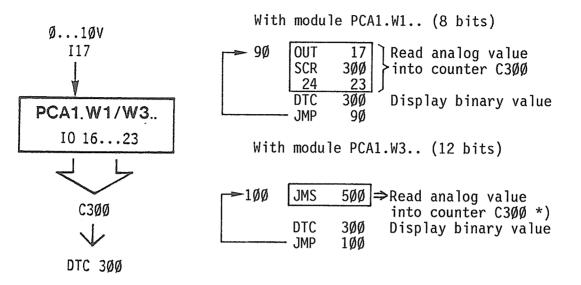

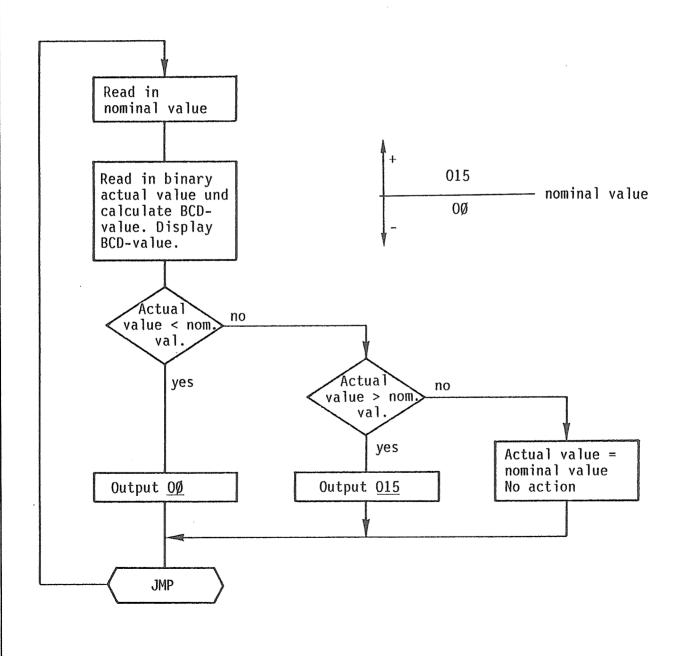

### Programming examples with analog modules

- Output of analog voltage from 8 to 12 inputs

Example of ramp voltage

Output of BCD values via modules PCA1.W12 (8 bits)

- or W32 (12 bits)

Reading an analog voltage into a counter register

- and display of the binary value with DTC On/off controller and floating controller (with analog module PCA1.W1.. or W3..)

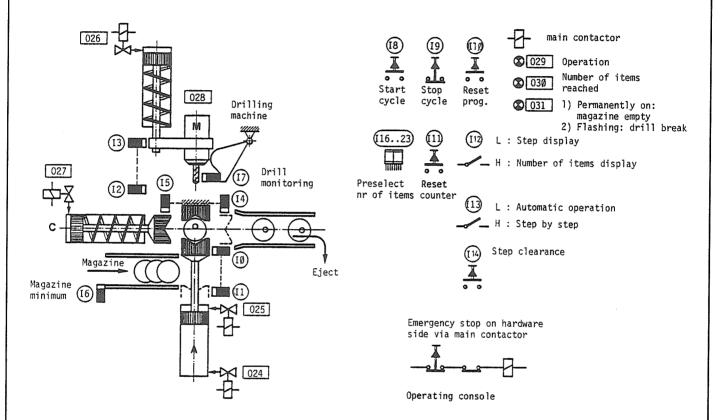

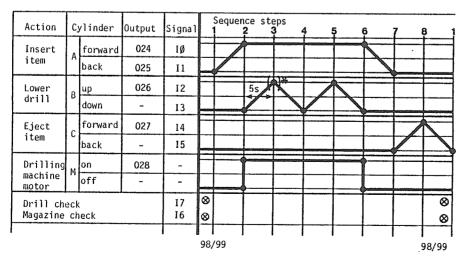

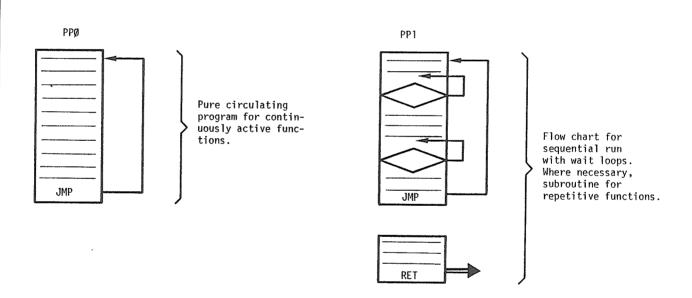

### Practical example

- A practical example using an automatic drilling machine

- 24.1 Dimensioning the PLC

- 24.1.1 Functions

- 24.1.2 Number of I/O

- 24.1.3 Type of I/O

- 24.1.4 Memory capacity

- 24.1.5 Displays

- 24.2 Programming

- 24.2.1 Program structure

- 24.2.2 Step control plan in accordance with DIN

- 24.2.3 Program preparation

## Procedure for solving a control problem by the introduction of a PLC

### PART F PROGRAMMING EXAMPLES

After defining the instruction set 1H in part E, the following collection of examples shows their interrelation. These are mainly typical examples which explain functions and use of the individual commands. The last example being an overall program of a practical application.

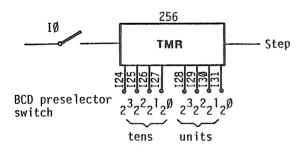

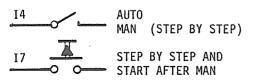

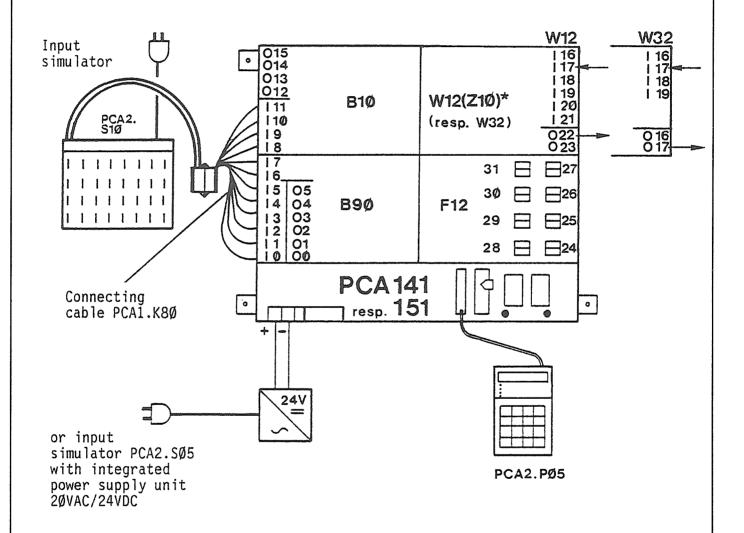

I/O adressing has been selected so that all examples can be reconstructed on a PCA1 or PCA2 with the aid of a PCA2.S1Ø input simulation unit. Accordingly, the address range is as follows:

$$I = \emptyset ...31$$

0 = 32...63

## Example 1: AND/OR linkage with ladder diagram

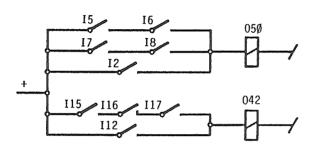

### 1) Parallel branchings

| Step                             | Instruct                                                                                              | Acting on                                                      |                                              |                                   |

|----------------------------------|-------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|----------------------------------------------|-----------------------------------|

|                                  | Description                                                                                           | In mnemo<br>code<br>(numerical)                                | element<br>or<br>step                        | resp.<br>OPERAND                  |

| 1Ø<br>11<br>12<br>13<br>14<br>15 | Start with interrogate AND-linkage AND-linkage OR-linkage AND-linkage Transfer result Return to start | STH (Ø1) ANH (Ø3) ANH (Ø3) ORH (Ø5) ANH (Ø3) OUT (1Ø) JMP (2Ø) | I1<br>I2<br>I3<br>I4<br>I5<br>O32<br>STEP 10 | 1<br>2<br>3<br>4<br>5<br>32<br>10 |

STEP

WHAT

WHERE

1 2 3 4

1 2 3 4

STEP

CODE

OPERAND

### 2) OR has priority over AND

For combinations of OR and AND functions it is necessary to refer to a special feature explained by means of this example.

The following contact configuration must be programmed:

The circuit cannot be programmed in this way because in accordance with the definition, the OR function of a parallel circuit corresponds to the following linkage branch. Otherwise it would correspond to the following schematic diagram:

There are two ways of programming the circuit:

- By the intermediate storage of the OR result

| ************************************** |     |      |                                             |

|----------------------------------------|-----|------|---------------------------------------------|

| ADDR NC                                | MNC | OPRD |                                             |

| 40 01                                  | STH | 2    | INTERROGATE 12 IF H                         |

| 41 05                                  | ORH | 3    | PARALLEL SWITCHING OF 13; INTERROGATE IF H  |

| 42 10                                  | OUT | 500  | STORE INTERMEDIATE RESULT IN A FLAG         |

|                                        |     |      |                                             |

| 43 01                                  | STH | 500  | NEW LINKAGE LINE WITH INTERROGATION OF FLAG |

| 44 03                                  | ANH | 1    | AND - LINKAGE WITH I1; INTERROGATED IF H    |

| 45 10                                  | OUT | 32   | ACCEPTANCE OF RESULT AT 032                 |

| 46 20                                  | JMP | 40-  | 1                                           |

|                                        |     |      |                                             |

|                                        |     |      |                                             |

- By re-drawing the circuit as a directly programmable parallel circuit with continuous parallel branches.

The second I1 contact is only for programming purposes. In reality I1 only exists once, in the program however, it is interrogated twice.

| ADDR | NC            | MNC | OPRD |                                                    | 7 |

|------|---------------|-----|------|----------------------------------------------------|---|

| 50   | $\mathbf{O1}$ | STH | 1    | START OF 1ST LINKAGE BRANCH                        | 1 |

| 51   | 03            | ANH | 2    |                                                    | ١ |

| 52   | 05            | ORH | 1    | PARALLEL SWITCHING AND START OF 2ND LINKAGE BRANCH | ١ |

| 53   | 03            | ANH | 3    |                                                    | 1 |

| 54   | 10            | OUT | 32   |                                                    | 1 |

| 55   | 20            | JMP | 50-  | >                                                  | ı |

|      |               |     |      |                                                    | 1 |

|      |               |     |      |                                                    | _ |

### Example 2: AND/OR-linkage with logic diagram

### 1) AND function

Logic diagram:

Ladder diagram:

The logic diagram facilitates clear representation of the logical linkages and signal states.

Representation of the following functions in the ladder diagram is problematic. For this reason use is frequently made in practice of the symbolic contacts. Here, the linkage is performed (032 activated) when I1 and I2 = H and I3 = L.

```

ADDR NC

MNC

OPRD

60 01

STH

INTERROGATE I1 IF H

61 03

ANH

AND - LINKAGE SUCCESSFUL (ACCU = 1) WHEN I2 = H

62 04

ANL

3

AND - LINKAGE SUCCESSFUL (ACCU = 1) WHEN I3 = L

63 10

OUT

32

64 20

JMP

60→>

```

When programming with a logic diagram the non-inverted elements are interrogated and linked with STH, ANH, ORH, the inverted elements with STL, ANL, ORL.

### 2) AND/OR combined

```

ADDR NC

MNC

OPRD

70 01

STH

1

71 03

ANH

2

7

72 04

ANL

ORL.

73 06

6

NEW, PARALLEL LINKAGE BRANCH

74 03

5

ANH

75 05

9

NEW, PARALLEL LINKAGE BRANCH

ORH

76 10

OUT

32

77 20

70->

JMP

```

### Example 3: EXOR-linkages

### 1) Comparison for inequality of logical states